## **ALAGAPPA UNIVERSITY**

[Accredited with 'A+' Grade by NAAC (CGPA:3.64) in the Third Cycle and Graded as Category–I University by MHRD-UGC] State University Established by the Government of Tamil Nadu)

#### **KARAIKUDI - 630 003**

### **DIRECTORATE OF DISTANCE EDUCATION**

# M.Sc. PHYSICS

**III -SEMESTER**

34533

# MICROPROCESSOR AND ELECTRONIC INSTRUMENTATION

Copy Right Reserved

For Private use only

#### Author

Dr. K. Sankaranarayanan, M.Sc., M.Phil., Ph.D.,

Professor Department of Physics Alagappa University Karaikudi– 630003. (Units: 1-7)

(UIIIS. 1-7)

#### Author

Dr. M. Ramesh Prabhu, M.Sc, Ph.D.,

Assistant Professor Department of Physics Alagappa University Karaikudi– 630003. (Units: 8-14)

"The Copyright shall be vested with Alagappa University"

All rights reserved. No part of this publication which is material protected by this copyright notice may be reproduced or transmitted or utilized or stored in any form or by any means now known or hereinafter invented, electronic, digital or mechanical, including photocopying, scanning, recording or by any information storage or retrieval system, without prior written permission from the Alagappa University, Karaikudi, Tamil Nadu.

# **SYLLABI-BOOK MAPPING TABLE**

## MICROPROCESSOR AND ELECTRONIC INSTRUMENTATION

| Syllabi                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mapping in Book |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| UNIT I 8085 ARCHITECTURE  Introduction -Intel 8085 - Architecture of Intel 8085 -Timing Diagram -Timing Diagram for opcode fetch cycle of 8085 - Timing Diagram for memory read cycle -Timing diagram for memory write cycle - I/O read and I/O write -Instruction set - Instruction and data formats - Addressing modes of 8085 - Status flags - Instruction set classification - Data transfer - Arithmetic operations - Logical operations - Branching operations -Interrupts | Pages 1 - 16    |

| UNIT II 8086 ARCHITECTURE Introduction - Architecture of 8086 - 8086 pin diagram - Pin description and functions - Register organization - Maximum mode function of 8086 - Minimum mode system                                                                                                                                                                                                                                                                                   | Pages 17 - 27   |

| UNIT III 8085 INSTRUCTIONS  Introduction to instructions for 8085 - Instruction set - Software development tools - Sample programs - Assembly language program for addition of two 8-bit numbers and store the sum - Assembly language program for 8-bit decimal subtraction and store the result - Assembly language program to shift an 8-bit number left by one bit - Assembly language program to find larger of two numbers                                                 | Pages 28 - 32   |

| UNIT IV INTERRUPTS AND STACK OPERATIONS OF 8085  Introduction - interrupts in 8085 - Interrupt service subroutine (ISS) - Subroutine - Flowcharting - Loops - Pseudo-instructions -Stack operations -Programming and applications: traffic control system                                                                                                                                                                                                                        | Pages 33-41     |

| UNIT V MICROCONTROLLER 8051  Introduction to 8 bit microcontrollers - 8051 microcontroller architecture - Features of 8051 microcontroller - Pin diagram of 8051 microcontroller - 8051 Memory organization - General purpose registers- Special Function Register- Oscillator and clock circuit- 8051 Addressing modes- 8051 Interrupts of 8051                                                                                                                                 | Pages 42 - 56   |

| UNIT VI 8051 - INSTRUCTION SET AND PROGRMMING Introduction to 8051 instruction set - Types of instructions - Data transfer instructions - Arithmetic instructions - Logical instructions - Boolean or bit manipulation instructions - Program branching instructions - Programming of 8051                                                                                                                                                                                       | Pages 57 - 63   |

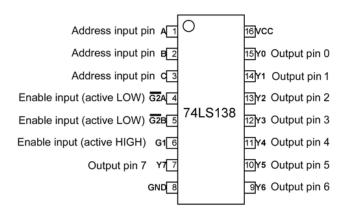

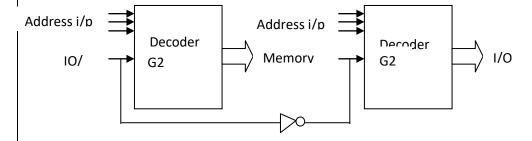

| UNIT VII - INTRODUCTION TO INTERFACING DEVICES Introduction - Address space partitioning- Memory mapped I/O                                                                                                                                                                                                                                                                                                                                                                      | Pages 64-73     |

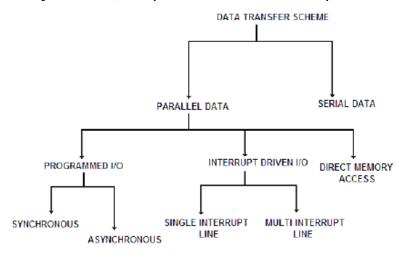

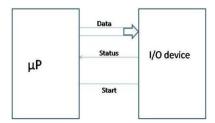

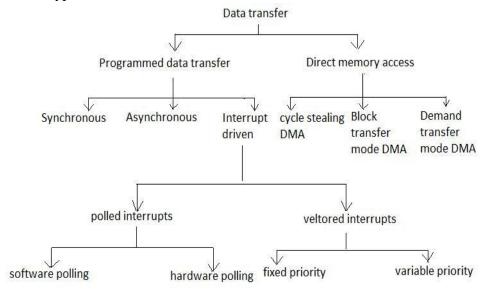

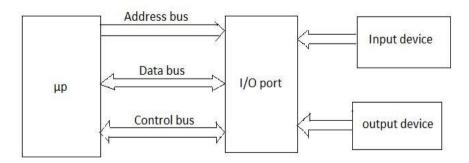

| interfacing - I/O interfacing - Data transfer schemes - Serial I/O mode transfer - Parallel data transfer scheme - Programmed data transfers - DMA data transfer scheme - Interrupts - I/O ports                                                                                                                                                                                                                                                                                                                     |                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| UNIT VIII -INTERFACING DEVICES (8255 AND 8259)  Programmable peripheral interface (PPI) - Intel 8255 - Control word - Internal architecture of Intel 8255 - Pin configuration of 8255 - Programmable interrupt controller (PIC) - Internal architecture of 8259                                                                                                                                                                                                                                                      | Pages 74- 83    |

| UNIT IX - INTERFACING DEVICES (8257 AND 8251) Introduction to DMA controller - Features of 8257 - Architecture of 8257 - Programmable communication interface: Intel 8251 - Pin description of 8251 USART - Architecture of Intel 8051A                                                                                                                                                                                                                                                                              | Pages 84 - 92   |

| UNIT X MICROPROCESSOR APPLICATIONS  Analog to Digital Data Converter - Microprocessor Based Temperature Monitoring Controller - Stepper Motors                                                                                                                                                                                                                                                                                                                                                                       | Pages 93 -100   |

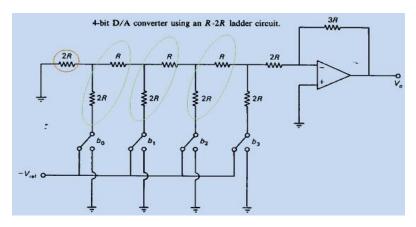

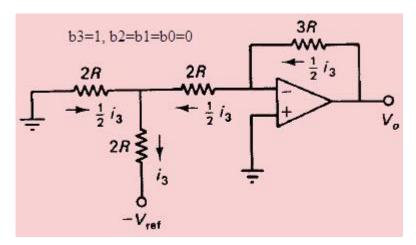

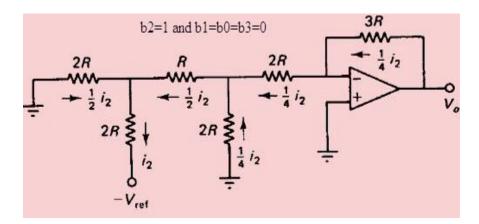

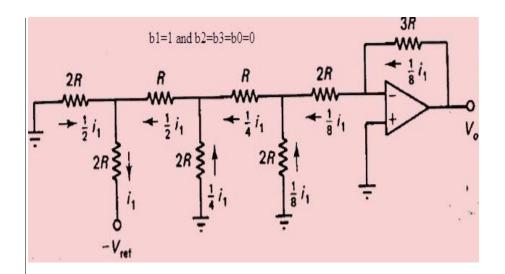

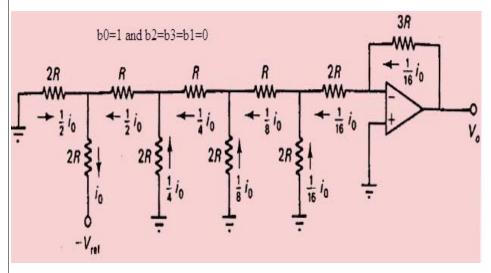

| UNIT XI AMPLIFIERS AND COMPARATORS  Introduction to instrumentation amplifier - Operation of instrumentation amplifier - Sample and hold circuit - Comparators - Digital to analog converter - D/A converter architectures - Weighted Resistor method - Resistor Ladder Network Method                                                                                                                                                                                                                               | Pages 101 - 108 |

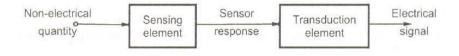

| UNIT XII TEMPERATURE TRANSDUCERS Introduction - Classification of transducers                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pages 109 - 111 |

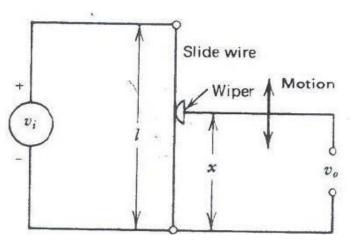

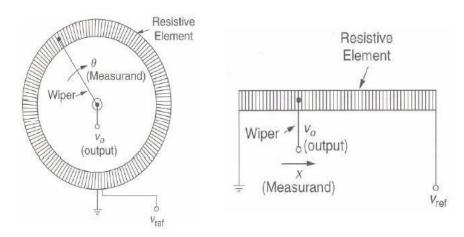

| UNIT XIII DISPLACEMENT TRANSDUCERS  Introduction- potentiometer - Types of potentiometer - Wire-wound type potentiometer - Thin film type potentiometer - Some of the advantages of the potentiometer - Some of the disadvantages of the potentiometer - Some of the applications of the potentiometer - Strain gauge - Resistive strain gauge - Capacitive transducers - Linear Variable Differential Transformer (LVDT) - Construction of LVDT - Advantages of LVDT - Disadvantages of LVDT - Applications of LVDT | Pages 112 - 118 |

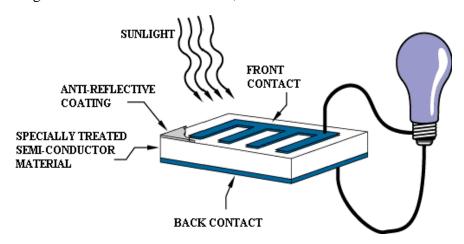

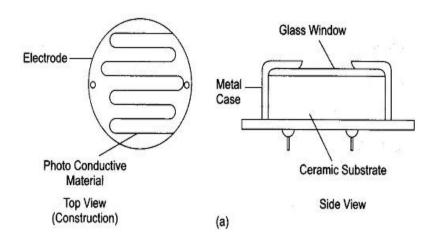

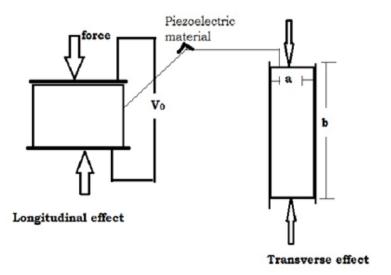

| UNIT XIV PHOTOELECTRIC TRANSDUCERS  Photoelectric transducer - Photo-voltaic cell - Types of photovoltaic cell- Photoconductive cell - Piezo-electric transducer - Piezoelectric effect- Working principle of piezoelectric transducer                                                                                                                                                                                                                                                                               | Pages 119 - 123 |

scheme - I/O mapped I/O scheme - Interfacing devices - Memory

| CONTENTS                                                                        |        |

|---------------------------------------------------------------------------------|--------|

| UNIT I – 8085 ARCHITECTURE                                                      | 1-16   |

| 1.1 Introduction                                                                |        |

| 1.2 Intel 8085                                                                  |        |

| 1.3 Architecture of Intel 8085                                                  |        |

| 1.4 Timing Diagram                                                              |        |

| 1.4.1 Timing Diagram for opcode fetch cycle of 8085                             |        |

| 1.4.2 Timing Diagram for memory read cycle                                      |        |

| 1.4.3 Timing diagram for memory write cycle                                     |        |

| 1.5 I/O read and I/O write                                                      |        |

| 1.6 Instruction set                                                             |        |

| 1.6.1 Instruction and data formats                                              |        |

| 1.7 Addressing modes of 8085                                                    |        |

| 1.8 Status flags                                                                |        |

| 1.9 Instruction set classification                                              |        |

| 1.9.1 Data transfer                                                             |        |

| 1.9.2 Arithmetic operations                                                     |        |

| 1.9.3 Logical operations                                                        |        |

| 1.9.4 Branching operations 1.9.5 Interrupts                                     |        |

| 1.9.5 Interrupts                                                                |        |

| UNIT II – 8086 ARCHITECTURE                                                     | 17-27  |

| 2.1 Introduction                                                                |        |

| 2.2 Architecture of 8086                                                        |        |

| 2.3 8086 pin diagram                                                            |        |

| 2.3.1 Pin description and functions                                             |        |

| 2.4 Register organization                                                       |        |

| 2.5 Maximum mode function of 8086                                               |        |

| 2.6 Minimum mode system                                                         |        |

|                                                                                 |        |

| UNIT III – 8085 INSTRUCTIONS                                                    | 28-32  |

| 3.1 Introduction to instructions for 8085                                       |        |

| 3.2 Instruction set                                                             |        |

| 3.3 Software development tools                                                  |        |

| 3.4 Sample programs                                                             |        |

| 3.4.1 Assembly language program for addition of two 8-bit numbers and store the | ie sum |

| 3.4.2 Assembly language program for 8-bit decimal subtraction and store the res | sult   |

| 3.4.3 Assembly language program to shift an 8-bit number left by one bit        |        |

| 3.4.4 Assembly language program to find larger of two numbers                   |        |

| UNIT IV- INTERRUPTS AND STACK OPERATIONS OF 8085                                | 33-41  |

| <ul> <li>4.2 Interrupt service subroutine (ISS)</li> <li>4.3 Subroutine</li> <li>4.4 Flowcharting</li> <li>4.5 Loops</li> <li>4.6 Pseudo-instructions</li> <li>4.7 Stack operations</li> <li>4.8 Programming and applications: traffic control system</li> </ul>                                                                                                                                                                                                                                                                                                                    |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

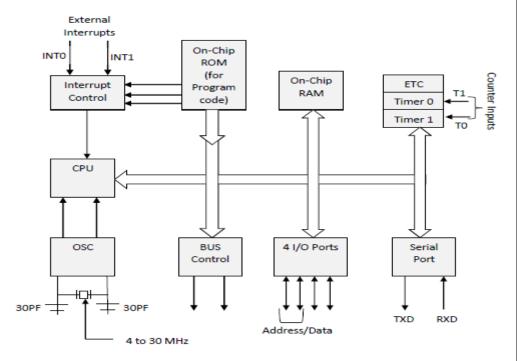

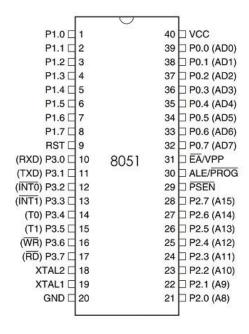

| UNIT V – MICROCONTROLLER 8051                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42-56 |

| <ul> <li>5.1 Introduction to 8 bit microcontrollers</li> <li>5.2 8051 microcontroller architecture</li> <li>5.3 Features of 8051 microcontroller         <ul> <li>5.3.1 Pin diagram of 8051 microcontroller</li> </ul> </li> <li>5.4 8051 Memory organization</li> <li>5.5 General purpose registers         <ul> <li>5.5.1 Special Function Register</li> </ul> </li> <li>5.6 Oscillator and clock circuit</li> <li>5.7 8051 Addressing modes</li> <li>5.8 8051 Interrupts of 8051</li> </ul>                                                                                      |       |

| UNIT VI –8051 - INSTRUCTION SET AND PROGRAMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57-63 |

| <ul> <li>6.1 Introduction to 8051 instruction set</li> <li>6.2 Types of instructions <ul> <li>6.2.1 Data transfer instructions</li> <li>6.2.2. Arithmetic instructions</li> <li>6.2.3 Logical instructions</li> <li>6.2.4 Boolean or bit manipulation instructions</li> <li>6.2.5 Program branching instructions</li> </ul> </li> <li>6.3 Programming of 8051</li> </ul>                                                                                                                                                                                                            |       |

| UNIT VII- INTRODUCTION TO INTERFACING DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64-73 |

| <ul> <li>7.1 Introduction</li> <li>7.2 Address space partitioning         <ul> <li>7.2.1 Memory mapped I/O scheme</li> <li>7.2.2 I/O mapped I/O scheme</li> </ul> </li> <li>7.3 Interfacing devices         <ul> <li>7.3.1 Memory interfacing</li> <li>7.3.2 I/O interfacing</li> </ul> </li> <li>7.4 Data transfer schemes         <ul> <li>7.4.1 Serial I/O mode transfer</li> <li>7.4.2 Parallel data transfer scheme</li> <li>7.4.2.1 Programmed data transfers</li> <li>7.4.2.2 DMA data transfer scheme</li> </ul> </li> <li>7.5 Interrupts</li> <li>7.6 I/O ports</li> </ul> |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

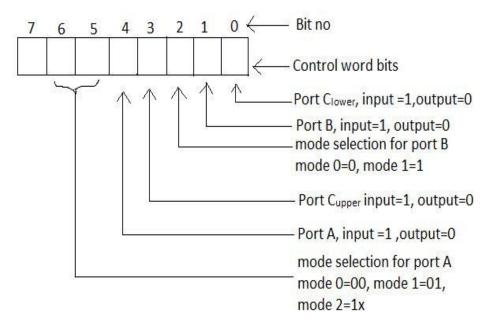

| UNIT VIII – INTERFACING DEVICES (8255 AND 8259)                                            | 74-83     |

|--------------------------------------------------------------------------------------------|-----------|

| 8.1 Programmable peripheral interface (PPI) 8.2 Intel 8255                                 |           |

| 8.3 Control word                                                                           |           |

| 8.4 Internal architecture of Intel 8255                                                    |           |

| 8.4.1 Pin configuration of 8255<br>8.5 Programmable interrupt controller (PIC)             |           |

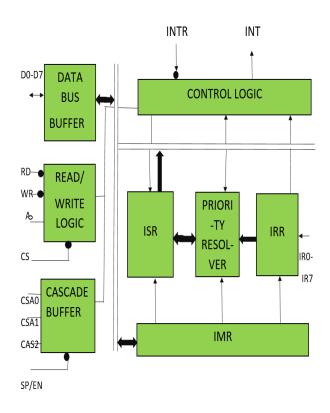

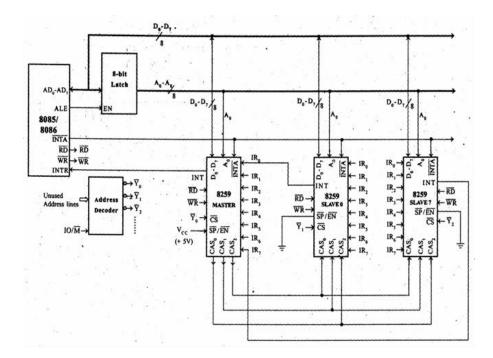

| 8.6 Internal architecture of 8259                                                          |           |

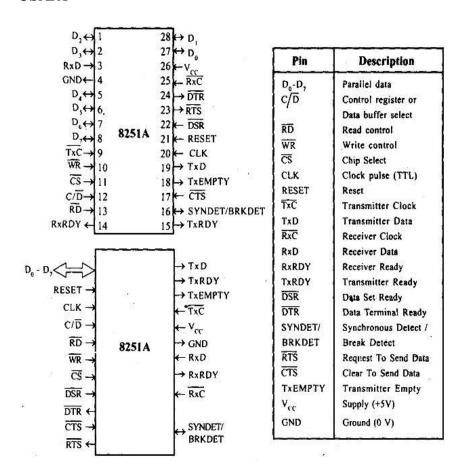

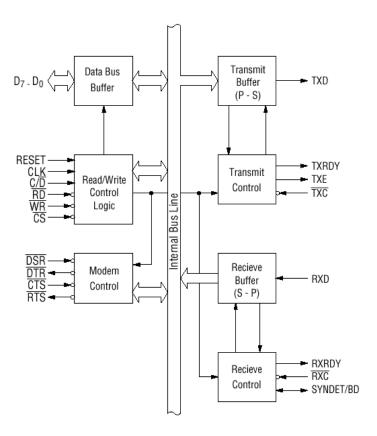

| UNIT IX -INTERFACING DEVICES (8257 AND 8251)                                               | 84-92     |

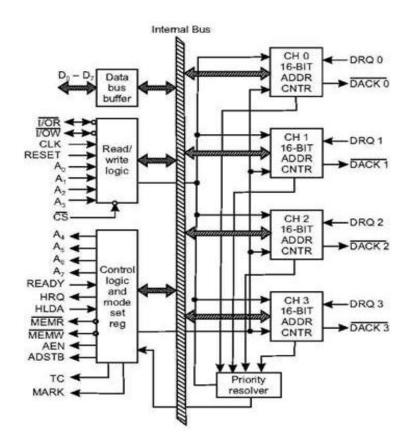

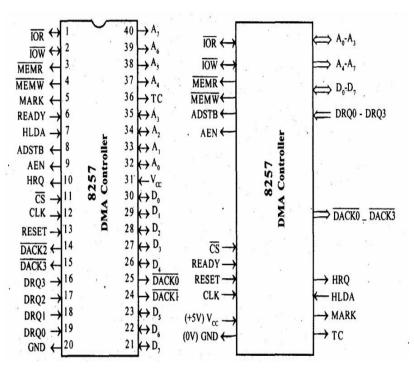

| 9.1 Introduction to DMA controller                                                         |           |

| 9.1.1 Features of 8257                                                                     |           |

| 9.1.2 Architecture of 8257                                                                 |           |

| 9.2 Programmable communication interface: Intel 8251                                       |           |

| 9.2.1 Pin description of 8251 USART 9.2.2 Architecture of Intel 8051A                      |           |

| 7.2.2 i nomectare of inter out 111                                                         |           |

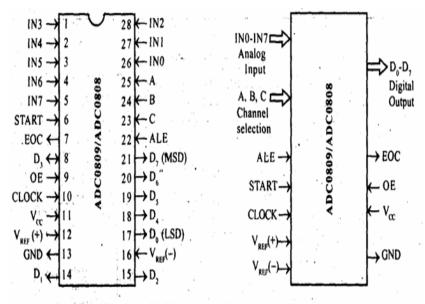

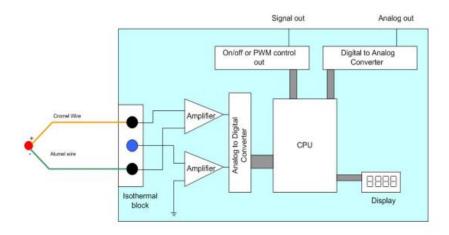

| UNIT X-MICROPROCESSOR APPLICATIONS                                                         | 93-100    |

| 10.1 Analog to Digital Data Converter                                                      |           |

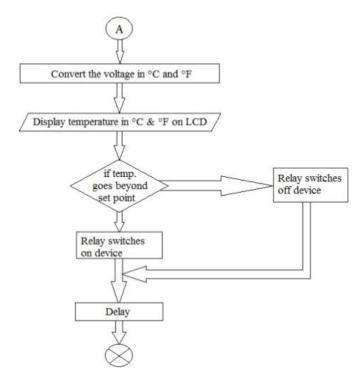

| 10.2 Microprocessor Based Temperature Monitoring Controller                                |           |

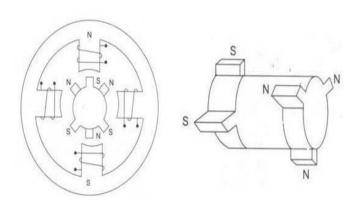

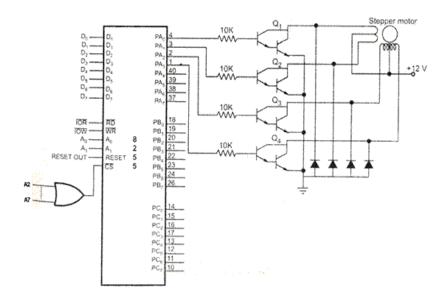

| 10.3 Stepper Motors                                                                        |           |

| UNITXI- AMPLIFIERS AND COMPARATORS                                                         | 101-108   |

|                                                                                            |           |

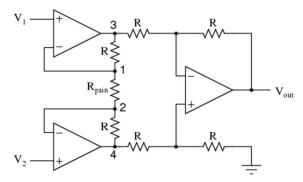

| 11.1 Introduction to instrumentation amplifier 11.2 Operation of instrumentation amplifier |           |

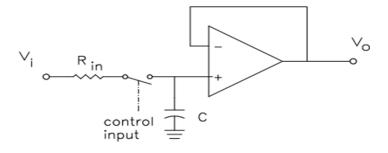

| 11.3 Sample and hold circuit                                                               |           |

| 11.4 Comparators                                                                           |           |

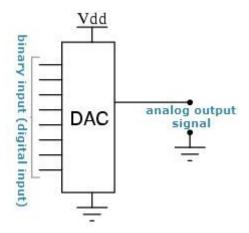

| 11.5 Digital to analog converter                                                           |           |

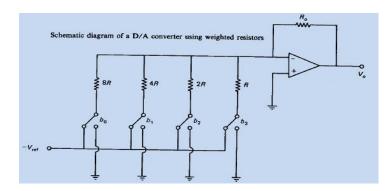

| 11.6 D/A converter architectures                                                           |           |

| 11.6.1 Weighted Resistor method<br>11.6.2 Resistor Ladder Network Method                   |           |

| 11.0.2 Resistor Eddder Network Method                                                      |           |

| UNIT XII – TEMPERATURE TRANSDUCERS                                                         | 108 - 114 |

| 12.1 Introduction                                                                          |           |

| 12.2 Classification of transducers                                                         |           |

| UNITXIII - DISPLACEMENT TRANSDUCERS                                                        | 112 - 118 |

| 13.1 Introduction- potentiometer                                                           |           |

| 13.2 Types of potentiometer                                                                |           |

| 13.2.1 Wire-wound type potentiometer                                                                                                                      |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 13.2.2 Thin film type potentiometer                                                                                                                       |           |

| 13.2.3 Some of the advantages of the potentiometer                                                                                                        |           |

| 13.2.4 Some of the disadvantages of the potentiometer are                                                                                                 |           |

| 13.2.5 Some of the applications of the potentiometer                                                                                                      |           |

| 13.3 Strain gauge                                                                                                                                         |           |

| 13.3.1 Resistive strain gauge                                                                                                                             |           |

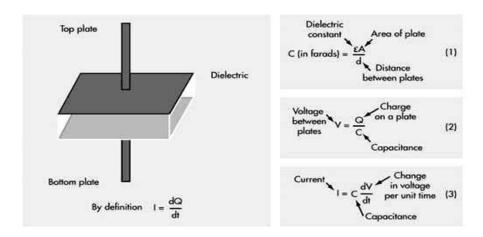

| 13.4 Capacitive transducers                                                                                                                               |           |

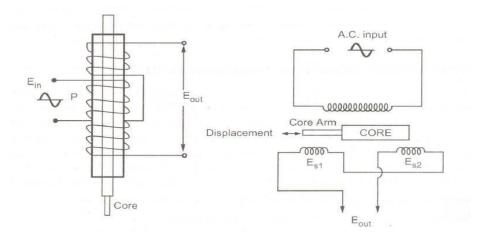

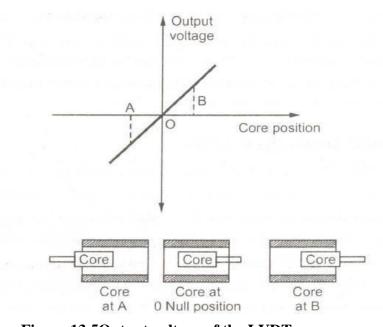

| 13.5 Linear Variable Differential Transformer (LVDT)                                                                                                      |           |

| 13.5.1 Construction of LVDT                                                                                                                               |           |

| 13.5.2 Advantages of LVDT                                                                                                                                 |           |

| 13.5.3 Disadvantages of LVDT                                                                                                                              |           |

| 13.5.4 Applications of LVDT                                                                                                                               |           |

|                                                                                                                                                           |           |

| UNIT XIV -PHOTOELECTRIC TRANSDUCERS                                                                                                                       | 119 - 123 |

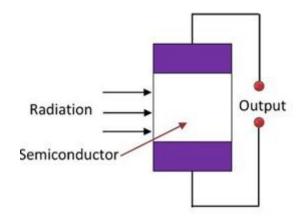

| UNIT XIV –PHOTOELECTRIC TRANSDUCERS  14.1 Photoelectric transducer                                                                                        | 119 - 123 |

|                                                                                                                                                           | 119 - 123 |

| 14.1 Photoelectric transducer                                                                                                                             | 119 - 123 |

| 14.1 Photoelectric transducer 14.2 Photo-voltaic cell                                                                                                     | 119 - 123 |

| <ul><li>14.1 Photoelectric transducer</li><li>14.2 Photo-voltaic cell</li><li>14.3 Types of photovoltaic cell</li></ul>                                   | 119 - 123 |

| <ul><li>14.1 Photoelectric transducer</li><li>14.2 Photo-voltaic cell</li><li>14.3 Types of photovoltaic cell</li><li>14.4 Photoconductive cell</li></ul> | 119 - 123 |

| 14.1 Photoelectric transducer 14.2 Photo-voltaic cell 14.3 Types of photovoltaic cell 14.4 Photoconductive cell 14.5 Piezo-electric transducer            | 119 - 123 |

# **UNIT – I 8085 ARCHITECTURE**

#### **Structure**

- 1.1 Introduction

- 1.2 Intel 8085

- 1.3 Architecture of Intel 8085

- 1.4 Timing Diagram

- 1.4.1 Timing Diagram for opcode fetch cycle of 8085

- 1.4.2 Timing Diagram for memory read cycle

- 1.4.3 Timing diagram for memory write cycle

- 1.5 I/O read and I/O write

- 1.6 Instruction set

- 1.6.1 Instruction and data formats

- 1.7 Addressing modes of 8085

- 1.8 Status flags

- 1.9 Instruction set classification

- 1.9.1 Data transfer

- 1.9.2 Arithmetic operations

- 1.9.3 Logical operations

- 1.9.4 Branching operations

- 1.9.5 Interrupts

#### 1.1 INTRODUCTION

Microprocessor is a controlling unit of a micro-computer, fabricated on a small chip capable of performing ALU (Arithmetic Logical Unit) operations and communicating with the other devices connected to it. Microprocessor consists of an ALU, register array, and a control unit. ALU performs arithmetical and logical operations on the data received from the memory or an input device. Register array consists of registers identified by letters like B, C, D, E, H, L and accumulator (A). The control unit controls the flow of data and instructions within the microprocessor.8085 is pronounced as "eighty-eighty-five" microprocessor. It is an 8-bit microprocessor designed by Intel in 1977 using NMOS technology. It has the following configuration:

- •8-bit data bus. One byte consists of 8- bits.

- 16-bit address bus, which can address upto 64KB

- A 16-bit program counter

- A 16-bit stack pointer

- Six 8-bit registers arranged in pairs: BC, DE, HLand can be used either individually or in pair

- Requires +5V supply to operate at 3.2 MHZ single phase clock It is used in many applications in different areas and some of them are washing machines, microwave ovens, mobile phones, etc.

#### 1.2 INTEL 8085

It is an 8 bit NMOS microprocessor and fabricated with forty pins IC(integrated circuit) package on a single LSI (Large scale Integration) chip. It uses a single +5 volt d.c(Direct Current) supply for its operation. It clock speed is 3 MHZ. It consists of 3 main architectural sections.

- 1-Arithmetic Logic Unit(ALU)

- 2-Timing and Control unit

- 3- Registers

#### **Arithmetic Logic Unit:**

It performs various arithmetic and logical operations like addition, subtraction, logical AND, logical OR, logical NOT, Increment and Decrement etc.

#### **Timing and Control unit:**

It generates timing and control signals which are necessary for the execution of the instructions. It also controls the peripherals and flow of data.

#### **Registers:**

Registers:- It is basically a collection of flip flops used to store a binary word. They are used by themicroprocessor or by the users for the temporary storage of data, manipulation of data and instructions.8085 has the following registers:

- 1-8 bit accumulator i.e. register A.

- 2- 6nos of 8 bits general purpose registers i.e. B,C,D,E,H,L.

- 3- 16 bit registers i.e. Stack Pointer (SP).

- 4-16 bit Program counter (PC), Status register, Temporary register and Instruction register.

The register A holds the operand during program execution.

The general purpose registers B,C,D,E,H,L are to handle either 8 or 16 bit data. Two 8 bit registers can be combined to handle 16 bit data. This is called register pair. Valid pairs of 8085 are B-C, D-E and H-L.The H-L pair is also used to address memory location denoted as M.

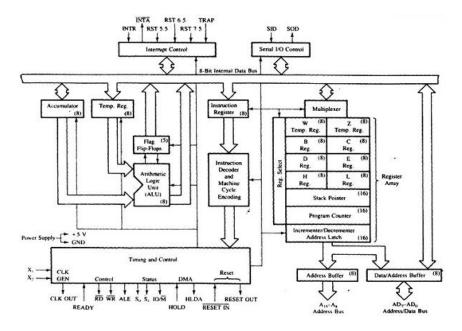

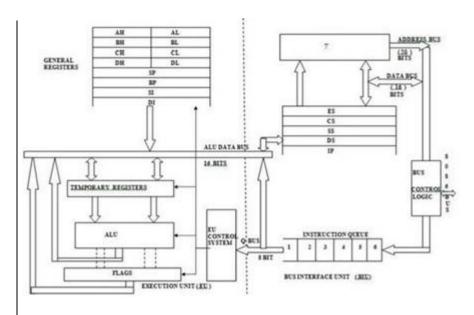

#### 1.3 ARCHITECTURE OF INTEL 8085

#### Address bus

A15-A8, it carries the most significant 8-bits of memory/IO address. One byte consists of 8- bits.

#### Address-Data bus

AD7-AD0, it carries the least significant 8-bit address and data in Multiplexed mode.

Figure 1.1 Architecture of Intel 8085

#### **Control and Status Signals**

These signals are used to identify the nature of operation going through the microprocessor. There are 3 control signal and 3 status signals.

Three control signals are RD, WR & ALE.

- **RD:** This signal indicates that the selected memory or IO device is to be read.

- **WR:** This signal indicates that the data on the bus is written into a selected memory or IO device.

- ALE: It is a positive going pulse generated when a new operation is started by the microprocessor. When the pulse goes high, it indicates address. When the pulse goes down it indicates data.

Three status signals are IO/M, S1& S0.

#### IO/M

This signal is used to differentiate between IO and Memory operations, i.e. when it is high; it indicates IO operation and when it is low then it indicates memory operation.

#### S1 & S0

These signals are used to identify the type of current operation. For example, if both S1 and S0 are 1, then it implies "FETCH" operation and if both S1 and S0 are 0, then it meant for "HALT".

#### **Power supply**

There are 2 power supply signals: VCC & VSS.

VCC indicates +5v power supply and VSS indicates ground signal.

#### **Clock signals**

There are 3 clock signals, i.e. X1, X2, CLK OUT.

- X1, X2: A crystal (RC, LC N/W) is connected at these two pins and is used to set frequency of the internal clock generator. This frequency is internally divided by 2.

- CLK OUT: This signal is used as the system clock for devices connected with the microprocessor.

#### **Interrupts & externally initiated signals**

Interrupts are the signals generated by the external devices to request the microprocessor to perform a task or to change the flow of execution of instructions. There are 5 interrupt signals, i.e. TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR. A detailed discussionon interrupts follows in the interrupts section.

- INTA: It is an interrupt acknowledgement signal.

- RESET IN: This signal is used to reset the microprocessor by setting the program counter to zero.

- RESET OUT: This indicates that the CPU is being reset and this signal is also used to reset all the connected devices when the microprocessor is reset.

- READY: This signal indicates that the device is ready to send or receive data. If READY is low, then the CPU has to wait for READY to go high.

- HOLD: This signal indicates that another device is requesting the use of the address and data buses.

- HLDA (HOLD Acknowledge): It indicates that the CPU has received the HOLD request and it will relinquish the bus in the next clock cycle. HLDA is set to low after the HOLD signal is removed.

#### Serial I/O signals

There are 2 serial signals, i.e. SID and SOD. These signals are used for serial communication between the microprocessor and the peripherals.

- SOD (Serial output data line): The output SOD is set/reset as specified by the SIM instruction.

- SID (Serial input data line): The data on this line is loaded into the accumulator whenever a RIM instruction is executed.

#### Stack pointer-SP

Stack is a sequence of memory locations defined by the programmer in LIFO (Last In First Out) logic. That is last data to be placed in the stack is the first one to be removed. The stack pointer –SP register contains the address of the stack top. It indicates the address of the data filled-up location. The address of the next available location is SP+1.

#### **Program counter-PC**

It is the address of the next instruction to be executed.

#### **Instruction register**

It holds a copy of the current instruction until it is decoded. It is not accessed by the user.

#### Status register and Temporary register

It contains the status flags of 8085 microprocessor.

It is used to store intermediate results and for intermediate calculations.

#### 1.4 TIMING DIAGRAM

It is a graphical representation of the steps which are carried out in a machine cycle for a particular operation of the microprocessor. It represents the pins (signals) involved in the operations and their status against each clock cycle.

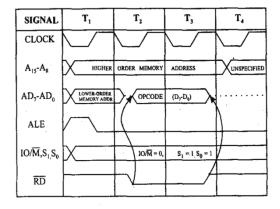

#### 1.4.1 TIMING DIAGRAM FOR OPCODE FETCH CYCLE OF 8085

Figure 1.2 Timing Diagram for Opcode Fetch Machine Cycle

- Opcode is a command given to the microprocessor in a machine language. Each instruction of the processor has one byte opcode.

- The opcodes are stored in in-built memory. The processor executes the opcode fetch machine cycle to fetch the opcode from memory for every instruction.

- The time taken by the processor to execute the opcode fetch cycle is 4T

- In this time, the first, 3 T-states are used for fetching the opcode from memory and the remaining T-states are used for internal operations by the processor.

| Machine | Period/ | Signal | Functions                                         |

|---------|---------|--------|---------------------------------------------------|

| Cycle   | Clock   |        |                                                   |

| M1      | T1      | IO/M   | = 0 - Address in the A15-A8 (MSB) and AD7-        |

|         |         |        | AD0 (LSB) Bars meant for Memory Address.          |

|         |         | A15-A8 | Carries 8 MSB bits                                |

|         |         | AD7-   | Carries 8 LSB bits, it works in multiplexed       |

|         |         | AD0    | mode.                                             |

|         |         | ALE    | = 1 - Address Latch Enable helps to latch         |

|         |         |        | AD7-AD0 $(8 - LSB)$ either in the memory or       |

|         |         |        | in an external latch in order to make AD7-        |

|         |         |        | AD0 available to transfer data in the next        |

|         |         |        | clock.                                            |

|         |         | S1 and | Both 1 meant for Fetch Operation                  |

|         |         | S0     |                                                   |

|         |         | RD     | = 1 means no read operation.                      |

|         | T2      | IO/M   | = 0 - Address in the A15-A8 (MSB) and AD7-        |

|         |         |        | AD0 (LSB) Bars meant for Memory Address           |

|         |         | A15-A8 | Carries 8 MSB Address bits                        |

|         |         | AD7-   | Carries 8 bits data, here opcode. Memory gets     |

|         |         | AD0    | opcode from the register and place it on this     |

|         |         |        | bus.                                              |

|         |         | ALE    | =0                                                |

|         |         | S1 and | Both 1 meant for Fetch Operation                  |

|         |         | S0     |                                                   |

|         |         | RD     | = 0 means Fetch operation. The data – opcode      |

|         |         |        | is placed in the data bus.                        |

|         | T3      | IO/M   | = 0 – Address in the A15-A8 (MSB)                 |

|         |         | A15-A8 | Carries 8 MSB Address bits                        |

|         |         | AD7-   | Carries 8 bits data, here opcode. It is placed in |

|         |         | AD0    | the instruction register (IR)                     |

|         |         | ALE    | =0                                                |

|         |         | S1 and | Both 1 meant for Fetch Operation                  |

|         |         | S0     |                                                   |

|         |         | RD     | = 1 means memory is disabled. The fetch           |

|         |         |        | operation is completed and the opcode is          |

|         |         |        | placed in the instruction register, IR.           |

| T4 | IO/M   | = remains 0                      |

|----|--------|----------------------------------|

|    | A15-A8 | No Data                          |

|    | AD7-   | No Data                          |

|    | AD0    |                                  |

|    | ALE    | =0                               |

|    | S1 and | Both 1 meant for Fetch Operation |

|    | S0     |                                  |

|    | RD     | = 1No Fetch Operation            |

|    |        | The opcode is decoded            |

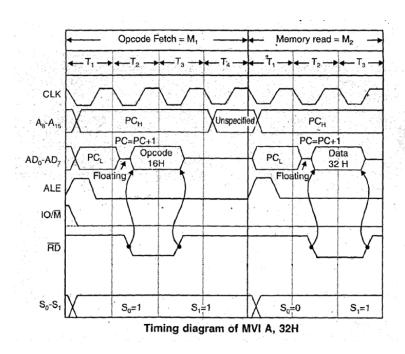

#### 1.4.2 TIMING DIAGRAM FOR MEMORY READ CYCLE

In a memory read cycle, the microprocessor reads the content of a memory location and the content is placed either in the accumulator or in any other CPU register. Ex-MVI A, 06H. For this instruction, the memory read cycle consumes 2 machine cycles, M1 and M2. In M1 the microprocessor completes the opcode fetch as described earlier and in M2 the microprocessor reads the content of a memory location. In the given example, the opcode is 3E and the data 06 will be placed in the register A. The timing diagram for Memory Read Cycle is given in the following figure.

Figure 1.3 Timing Diagram for Memory Read

In the above figure, the fetching of opcode is completed at the end of the machine cycle M1. In M2, the following operations are taking place in the microprocessor.

8085 Architecture

NOTES

If the length of the instruction is three bytes, it needs three machine cycles (M1, M2 and M3). For example, LXI D, 2500H instruction needs three machine cycles, to fetch the opcode, to read 8LSB of the data and to read 8MSB of the data. In the case of LDA 2500H, 4 machine cycles are needed to fetch the opcode, to read 8LSB of the address, to read 8MSB of the address and to transfer the content of the address to the Accumulator

| Machine | Period/ | Signal      | Functions                                           |

|---------|---------|-------------|-----------------------------------------------------|

| Cycle   | Clock   |             |                                                     |

| M2      | T1      | IO/M        | = 0 - Address in the A15-A8 (MSB) and AD7-          |

|         |         |             | AD0 (LSB) Bars meant for Memory Address.            |

|         |         | A15-        | Carries 8 MSB bits                                  |

|         |         | A8          |                                                     |

|         |         | AD7-<br>AD0 | Carries 8 LSB bits, it works in multiplexed mode.   |

|         |         | ALE         | = 1 - Address Latch Enable helps to latch           |

|         |         |             | AD7-AD0 (8 – LSB) either in the memory or in        |

|         |         |             | an external latch in order to make AD7-AD0          |

|         |         |             | available to transfer data in the next clock.       |

|         |         | S1 and      | S1=1 and S0=0 meant for Read Operation              |

|         |         | So and      | 31–1 and 30–0 meant for Read Operation              |

|         |         | RD          | _ 1 mans no read energion                           |

|         | T2      | IO/M        | = 1 means no read operation.                        |

|         | 12      | IO/IVI      | = 0 - Address/Data in the A15-A8 (MSB) and          |

|         |         |             | AD7-AD0 (LSB) Bars meant for Memory                 |

|         |         | A 1.5       | Address                                             |

|         |         | A15-        | Carries 8 MSB Address bits                          |

|         |         | A8          |                                                     |

|         |         | AD7-        | Carries 8 bits data, here data. Memory gets         |

|         |         | AD0         | opcode from the register and places it on this bus. |

|         |         | ALE         | = 0                                                 |

|         |         | S1 and      | S1=1 and S0=0 meant for Read Operation              |

|         |         | S0          | ar a man ar a sanan ar ar                           |

|         |         | RD          | = 0. It enables the memory for read operation       |

|         |         |             | and data is placed in the data bus.                 |

|         | T3      | IO/M        | = 0 – Address in the A15-A8 (MSB)                   |

|         |         | A15-        | Carries 8 MSB Address bits                          |

|         |         | A8          |                                                     |

|         |         | AD7-        | Carries 8 bits data, it is placed in the CPU.       |

|         |         | AD0         | 1                                                   |

|         |         | ALE         | = 0                                                 |

|         |         | S1 and      | S1=1 and S0=0 meant for Read Operation              |

|         |         | <b>S</b> 0  | 1                                                   |

|         |         | RD          | = 1 means memory is disabled. The read              |

|         |         |             | operation is completed and the data is placed in    |

|         |         |             | the CPU.                                            |

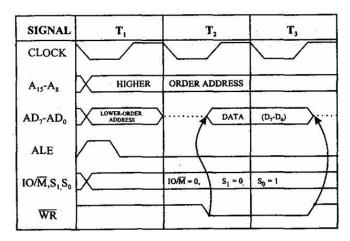

#### 1.4.3 TIMING DIAGRAM FOR MEMORY WRITE CYCLE

- In a memory write cycle the CPU sends data from the accumulator or any other register to memory.

- The status signal S0 and S1 are 1 and 0 respectively for write operation.

- The WR signal goes low in T2 indicating that the write operation is to be performed.

- During T2 the address/data bus is not disabledas in fetch or read operation but the data to be sent out to memory is placed on the address/data bus which works under multiplexed mode.

- In T3, the WR signal goes high indicating that the write operation is completed.

Example: - 1. MOV M, A and 2. STA 2400H

Figure 1.4 Timing Diagram for Memory Write cycle

#### 1.5 I/O READ AND I/O WRITE

In I/O read cycle, the data from the I/O device or I/O port is placed in the accumulator. The memory read and the I/O read cycles are very similar except that the IO/M signal is high which means that the address in the A bus is for an Input device or port. The IN instruction can be used and it is of 2 bytes long and requires 3 machine cycles. They are to fetch the opcode, to read the address of the IO device or IO port and to read the data from IO device or IO port. In I/O write cycle, the microprocessor sends the data to IO device or port. As like I/O read cycle, the IO/M is high indicating the address in the bus is for the IO device or port. The OUT instruction is used to send the data from the microprocessor to the IO device or port by executing three machine cycle. First is to fetch the opcode, second is to read the address of the IO device or IO port and the third is to write the data in the IO device or IO port.

#### 1.6 INSTRUCTION SET

8085 instruction set generally consists of the following types:

- Data transfer instructions.

- Arithmetic Instructions add, subtract, increment and decrement.

- Logical Instructions AND, OR, XOR and rotate.

- Branch Control Instructions –call, jump, return and restarts. Both conditional and unconditional jump, call and return instructions.

- In/Outinstructions and other instructions for setting/clearing flag bits, enabling/disabling interrupts, stack operations, etc.

#### 1.6.1 INSTRUCTION AND DATA FORMATS

Intel 8085 is an 8-bit microprocessor and canhandles 8-bit data. All the memory locations are designed to store 8-bit data. For, 16-bit data, consecutive memory locations are used. The address of memory location is of 16-bit i.e. 2 bytes.

The various techniques to specify data for instructions are:

- (1) 8-bit or 16-bit data may be given directly or through the address of the memory location, I/O port or I/O device, where data resides, in the instruction itself.

- (2) Instructions may specify with only one or two registers. Essentially, one of the operand is the accumulator and other operand is the content of the register.

The length of the instruction varies with the different ways of specifying data in the instruction. There are three types of instructions of Intel 8085 based on the length; (1)Single byte instruction, (2)2-byte instruction and (3)3-byte instruction.

#### **Single-Byte instruction**

The opcode and the operands are in the instruction itself. These instructions are of one byte.

Ex-MOV A, C; Move the content of register C to A

79H is the opcode for MOV A, C. The binary form of opcode 78H is 01111001. The first twobits i.e. 01 for MOV operation; the next 3 bits i.e. 111 for register A and last 3 bits 001are for register C.

#### **Two-Byte instruction**

In case of two byte instruction the 1st byte of the instruction is opcode and 2nd byte is either data or address. Both bytes should be stored in two consecutive memory locations.

Ex-MVI C, 05; Move the data 05 to register C

MVI C,05 in the code form is 0E 05. The 1st byte i.e. 0E is the opcode for MVI C and 2nd byte i.e. 05 is the data which is to be moved to register C.

#### Three-Byte instruction

The three byte instruction has the 1st byte as opcode and 2nd and 3rd bytesare either 16-bit data or 16-bit address. They should be stored in three consecutive memory locations.

Ex- LDA 2500H, Load the accumulator with the content of the memory location, 2500H

In code form is 3A, 00, 25

The 1st byte, 3A is the opcode for LDA. The 2nd byte, 00 is 8 LSBs of addressand the 3rd byte, 25 is 8 MSBs ofaddress.

#### 1.7 ADDRESSING MODES OF 8085

Operands are very essential for an instruction to perform operations. There are various ways to specify the data for instructions. The various formats for specifying the operands are called addressing modes and in 8085 the following addressing modes are available.

- a) Direct addressing

- b) Register addressing

- c) Register indirect addressing

- d) Immediate addressing

- e) Implicit addressing

#### a) Direct addressing mode:

The address of the operand (data) is given in the instruction itself. For example, STA 2000H and IN 02H. In the first instruction, the data in the accumulator will be stored in the memory location, 2000H and the second instruction is used to read the data from the I/O port whose address is 02. The

source of the data and the destination for the data are explicitly given in these instructions.

#### b) Register addressing mode:

In this addressing mode the operands are in the general purpose register. The opcode specifies the address of the operand (registers) in addition to the operation to be executed.

Ex: 1. MOV B, A and 2. ADD C. In the example 1, the content of the register A will be moved to the register B. The opcode for this operation is 47H. It specifies the operation as well as the operands. In the example 2, the content of the register C will be added to the content of the register A and the result will be stored in the register A. The opcode for this operation is 81H. Again, this opcode specifies the operands and the operation.

#### c) Register indirect addressing mode:

In register indirect addressing mode, the operand is in the memory location and the address of the memory location resides in H-L register pair, as denoted by the letter "M". M denotes the content of the address stored in the H-L register pair.

For example: LXI H, 2100H - Load the H-L register pair with the content of 2100H

MOV A,M – Move the content of 2100H to the accumulator

ADD C – Add the content of the register C with A, Now A=A+C

HLT - Halt

In the above example, the instruction MOV A, M lists under register indirect addressing mode.

#### d) Immediate addressing mode:

Under immediate addressing mode, the operand is specified within the instruction itself. Further, the mnemonics contains the letter "I" as the last letter and the data is explicitly present in the instruction.

8085 Architecture

NOTES

Example: 1. MVI A,05H - Move immediate data 05H to Accumulator.

2. ORI 05H – Perform logical OR with data 05H and the content of the register A

#### e) Implicit addressing mode:

Instructions which operate on the content of the accumulator are listed under Implicit addressing mode. Here, the operand resides in the register A and do not require the address. RAL, RAR, CMA, CMC etc. are the examples.

#### 1.8 STATUS FLAGS

In 8085, there are 5 status flags and each of the flag holds 1 bit. The value of the bit will be either 0 or 1. These flags are used to follow certain condition which arises during the arithmetic and logical operations which ultimately sets the value of individual flag. It is a set of 5 flip-flops. They are

- i. Carry Flag(CS)

- ii. Sign Flag(S)

- iii. Zero Flag(Z)

- iv. Parity Flag(P)

- v. Auxiliary carry flag(AC)

#### **Carry Flag**

It holds carry out of the MSB resulting from the execution of an arithmetic operation. If there is a carry from addition or a borrow from subtraction or comparison, the carry flag is set to 1 otherwise 0.

#### Sign Flag

It is set to 1 if the MSB of the result of arithmetic or logical operation is 1 otherwise 0.

#### Zero Flag

It is set to 1 if the result of an arithmetic or logical operation is 0 otherwise 0 for non-zero result.

#### **Parity Flag**

The result of the operation contains even number of 1sset this flag to 1 otherwise 0 for odd number of 1s.

#### **Auxiliary Carry Flag**

It holds carry from bit 3 to 4 resulting from the execution of an arithmetic operation otherwise 0.

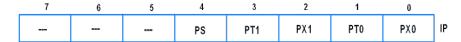

#### **Program Status Word (PSW)**

It is an 8-bit register out of which five bits indicate the 5 status flags and the remaining three bits are undefined. PSW and the accumulator treated as a 16 bit unit for stack operation.

#### 1.9 INSTRUCTION SET CLASSIFICATION

An instruction is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the instruction set, determines what functions the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

#### 1.9.1 DATA TRANSFER

This group of instructions copy data from a location called a source to another location called a destination, without modifying the content of the source. In technical manual, the term data transfer is used for this copying function. However, the term transfer is misleading; it creates the impression that the content of the source are destroyed when, in fact, the content are retained without any modification. The various types of data transfer (copy) are listed below together with examples of each type:

| Types                                    | Examples                              |

|------------------------------------------|---------------------------------------|

| 1. Between Registers.                    | 1. Copy the content of the register B |

|                                          | into                                  |

|                                          | register D. MOV D, B                  |

| 2. Specific data byte to a register or a | 2. Load register B with the data byte |

| memory location.                         | 32H.                                  |

|                                          | MVI B, 32H                            |

| 3. Between a memory location and a       | 3. From a memory location 2000H to    |

| register.                                | register                              |

|                                          | B.MOV B, M                            |

| 4. Between an I/O device and the         | 4.From an input port to the           |

| accumulator.                             | accumulator.                          |

|                                          | IN 02                                 |

#### 1.9.2 ARITHMETIC OPERATIONS

These instructions perform arithmetic operations such as addition, subtraction, increment, and decrement.

8085 Architecture

NOTES

**Addition -** Any 8-bit number, or the content of a register or the content of a memory location can be added to the content of the accumulator and the sum is stored in the accumulator. No two other 8-bit registers can be added directly (e.g., the content of register B cannot be added directly to the content of the register C). The instruction DAD is an exception; it adds 16-bit data directly in register pairs.

**Subtraction -** Any 8-bit number, or the content of a register, or the content of a memory location can be subtracted from the content of the accumulator and the result is stored in the accumulator. The subtraction is performed in 2's compliment, and the results if negative, are expressed in 2's complement. No two other registers can be subtracted directly.

**Increment/Decrement -** The 8-bit content of a register or a memory location can be incremented or decremented by 1. Similarly, the 16-bit content of a register pair (such as BC) can be incremented or decremented by 1. These increment and decrement operations differ from addition and subtraction in an important way; i.e., they can be performed in any one of the registers or in a memory locations.

#### 1.9.3 LOGICAL OPERATIONS

These instructions perform various logical operations with the content of the accumulator.

**AND, OR Exclusive-OR -** Any 8-bit number, or the content of a register, or of a memory location can be logically ANDed, ORed, or Exclusive-ORed with the content of the accumulator. The result is stored in the accumulator.

**Rotate-** Each bit in the accumulator can be shifted either left or right to the next position. **Compare-** Any 8-bit number or the content of a register, or a memory location can be compared for equality, greater than, or less than, with the content of the accumulator.

**Complement -** The content of the accumulator can be complemented. All 0s are replaced by 1s and all 1s are replaced by 0s.

#### 1.9.4 BRANCHING OPERATIONS

This group of instructions alters the sequence of program execution either conditionally or unconditionally.

**Jump -** Conditional jumps are an important aspect of the decision-making process in the programming. These instructions test for a certain conditions (e.g., Zero or Carry flag) and alter the program sequence when the condition is met. In addition, unconditional jump is also available.

**Call, Return, and Restart -** These instructions change the sequence of a program either by calling a subroutine or returning from a subroutine. The conditional Call and Return instructions also can test condition flags.

#### 1.9.5 INTERRUPTS

- The processor has 5 interrupts. They are presented below in the order of their priority (from lowest to highest):

- INTR is an interrupt request signal, maskable and 8080A compatible interrupt. When the interrupt occurs the processor completes the instruction at hand and goes to the CALL instruction. INTA will be sent by the microprocessor after receiving the INTR.

- One of the 8 RST instructions (RST0 RST7). The processor saves current program counter into stack and branches to memory location N \* 8 (where N is a 3-bit number from 0 to 7 supplied with the RST instruction).

- CALL instruction (3 byte instruction). The processor calls the subroutine whose addressis specified in the second and third bytes of the instruction.

- RST5.5 is a maskable interrupt. When this interrupt is received the processor saves the content of the PC register into stack and branches to 2CH address.

- RST6.5 is a maskable interrupt. When this interrupt is received the processor saves the content of the PC register into stack and branches to 34H address.

- RST7.5 is a maskable interrupt. When this interrupt is received the processor saves the content of the PC register into stack and branches to 3CH address.

- TRAP is a non-maskable interrupt. When this interrupt is received the processor saves the content of the PC register into stack and branches to 24H address.

- All maskable interrupts can be enabled or disabled using EI and DI instructions. RST 5.5, RST6.5 and RST7.5 interrupts can be enabled or disabled individually using SIM instruction.

# **UNIT – II 8086 ARCHITECTURE**

#### **Structure**

- 2.1 Introduction

- 2.2 Architecture of 8086

- 2.3 8086 pin diagram

- 2.3.1 Pin description and functions

- 2.4 Register organization

- 2.5 Maximum mode function of 8086

- 2.6 Minimum mode system

#### 2.1 INTRODUCTION

- A microprocessor is an Integrated Circuit with all the functions of a CPU however; it cannot be used stand-alone since unlike a microcontroller it has no memory or peripherals.8086 does not have a RAM or ROM inside it. It is a 16-bit Microprocessor (μp).

- It's ALU, internal registers works with 16bit binary word. 8086 has a 20 bit address bus and can access up to  $2^{20}$ = 1 MB memory locations. 8086 has a 16bit data bus. It can read or write data to a memory/port either 16bit or 8 bit at a time. It can support up to 64K I/O ports. It provides 14 numbers of 16 -bit registers.

- Clock frequency range of 8086 is 6-10 MHz. It has multiplexed address and data bus AD0- AD15 and an address bus A16 A19. It requires single phase clock with 33% duty cycle to provide internal timing.

- It can prefetch up to 6 instruction bytes from memory and queues them in order to speed up the instruction execution. It requires +5V power supply and built in a 40 pin dual in line package.

- 8086 is designed to operate in two modes, Minimum mode and Maximum mode. The minimum mode is selected by applying logic 1 to the MN  $/\overline{MX}$  input pin.

- This is a single microprocessor configuration. The maximum mode is selected by applying logic 0 to the MN /  $\overline{MX}$  input pin. This is capable of cascading with multi microprocessors configuration.

#### 2.2 ARCHITECTURE OF 8086

The following figure represents the internal architecture of 8086 which represents the register and bus organization.

Figure 2.1 Architecture of 8086

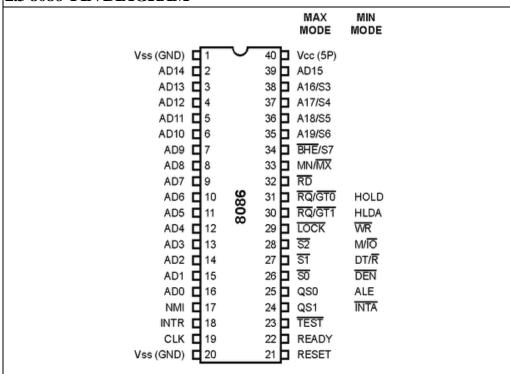

#### **2.3 8086 PIN DIAGRAM**

Figure 2.2 Pin diagram of 8086

#### 2.3.1 PIN DESCRIPTIONAND FUNCTIONS

#### Power supply and frequency signals

It uses 5V DC supply at  $V_{\text{CC}}$  pin 40, and uses ground at  $V_{\text{SS}}$  pin 1 and 20 for its operation.

#### **Clock signal**

Clock signal is provided through pin19. It provides timing to the processor for operations. Its clock frequency is different for different versions, i.e. 5MHz, 8MHz and 10MHz.

#### Address/data bus and Address/status bus

Pins AD0-AD15are 16 bit address/data bus. AD0-AD7 carries low order byte data and AD8-AD15 carries higher order byte data. During the first clock cycle, it carries 16-bit address and after that it carries 16-bit data once low order byte is latched in the memory.

Pins A16-A19/S3-S6arethe 4 bit address/status bus. During the first clock cycle, it carries 4-bit address and later it carries status signals.

#### $S7/\overline{BHE}$ and $\overline{RD}$

BHE stands for Bus High Enable. It is available at pin 34 and used to indicate the transfer of data using data bus D8-D15. This signal is low during the first clock cycle, thereafter it is active. The status signal S7 is available during T2, T3 and T4.

It is available at pin 32 and its value is 0 during Read operation.

#### **READY and RESET**

It is available at pin 22. It is an acknowledgement signal from I/O devices to the microprocessor for data transfer. It is an active high signal. When it is high, it indicates that the device is ready to transfer data. When it is low, it indicates wait state.

It is available at pin 21 and is used to restart the execution. It causes the processor to immediately terminate its present activity. This signal is active high for the first 4 clock cycles to RESET the microprocessor.

#### **INTR and INTA**

It is available at pin 18. It is an interrupt request signal from the I/O devices, which is sampled during the last clock cycle of each instruction to determine if there is any interrupt request or not.

It is an interrupt acknowledgement signal and is available at pin 24. When the microprocessor receives this signal, it acknowledges the interrupt by raising this signal to 1.

#### **NMI**

It stands for non-maskable interrupt and is available at pin 17. It is an edge triggered input, which causes an interrupt request to the microprocessor.

#### TEST

8086 Architecture

NOTES

This signal is like wait state and is available at pin 23. When this signal is high, then the processor has to wait in IDLE state, else the execution continues.

#### $MN/\overline{MX}$

It stands for Minimum/Maximum mode operation and is available at pin 33. It dictates the mode of operation of the processor; when it is high, it works in the minimum mode else 0 for maxi mode.

#### **ALE**

It stands for address latch enable and is available at pin 25. A positive pulse is generated each time the processor begins any operation. This signal indicates the availability of a valid address on the address/data bus.

#### DENandDT/R

It stands for Data Enable and is available at pin 26. It is used to enable Trans-receiver 8286. The trans-receiver is a device used to separate data from the address/data bus.

It stands for Data Transmit/Receive signal and is available at pin 27. It decides the direction of data flow through the trans-receiver. When it is high, data is transmitted out and vice-a-versa.

#### $M/\overline{10}$

This signal is used to distinguish between memory and I/O operations. When it is high, it indicates memory access operation else 0 for I/O access operation. It is available at pin 28.

#### $QS_1$ and $QS_0$

These are queue status signals and are available at pin 24 and 25. These signals provide the status of instruction queue. Their conditions are shown in the following table -

| $QS_0$ | $QS_1$ | Status                              |

|--------|--------|-------------------------------------|

| 0      | 0      | No operation                        |

| 0      | 1      | First byte of opcode from the queue |

| 1      | 0      | Empty the queue                     |

| 1      | 1      | Subsequent byte from the queue      |

It stands for write signal and is available at pin 29. It is used to write the data into the memory or to the output device depending on the status of  $M/\overline{IO}$  signal.

#### **LOCK**

When this signal is active, it indicates to the other processors not to ask the CPU to leave the system bus. It is activated low using the LOCK prefix on any instruction and is available at pin 29.

#### RQ/GT<sub>1</sub>, HOLD and RQ/GT<sub>0</sub>, HLDA

These are the Request/Grant signals (Pins 30 and 31) used by the other processors requesting the CPU to release the system bus. When the signal is received by CPU, then it sends acknowledgment.  $RQ/GT_0$  has a higher priority than  $RQ/GT_1$ .

#### **HLDA**

It stands for Hold Acknowledgement signal and is available at pin 30. This signal acknowledges the HOLD signal.

#### **HOLD**

This active HIGH signal indicates the processor that an external device is requesting to access the address/data buses. It is available at pin 31.

#### $S_0, S_1, S_2$

These are the status signals that provide the status of operation, which is used by the Bus Controller 8288 to generate memory & I/O control signals. These are available at pin 26, 27, and 28. Following is the table showing their status –

| $S_2$ | $S_1$ | $S_0$ | Status                    |

|-------|-------|-------|---------------------------|

| 0     | 0     | 0     | Interrupt acknowledgement |

| 0     | 0     | 1     | I/O Read                  |

| 0     | 1     | 0     | I/O Write                 |

| 0     | 1     | 1     | Halt                      |

| 1     | 0     | 0     | Opcode fetch              |

| 1     | 0     | 1     | Memory read               |

| 1 | 1 | 0 | Memory write |

|---|---|---|--------------|

| 1 | 1 | 1 | Passive      |

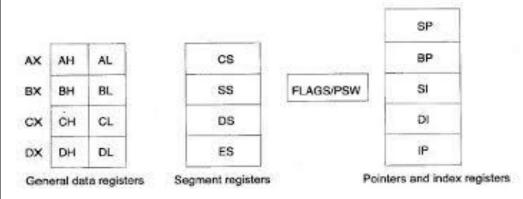

#### 2.4 REGISTER ORGANIZATION

The registers in 8086 are grouped as follows;

- Pointers and index registers

- Segment registers

- Instruction Pointer and Status Flags

- General data registers.

Intel 8086 uses 20 bit address lines. So its memory capacity is  $(2^{20}) = 1$ MB of memory. Memory segmentation is first introduced in this type of microprocessor. All the registers of 8086 are 16-bit registers. The general purpose registers can be used as either 8-bit register or 16-bit register. The register set of 8086 can be categorized into 4 different groups.

Figure 2.3 Organizations of Registrar

#### General data registers

- The registers AX, BX,CX and DX are the general purpose 16-bit registers. AX is used as 16-bit accumulator. Accumulator can be used for I/O operations, rotate and string manipulation.

- The lower 8-bit is designated as AL (accumulator) and higher 8-bit is designated as AH. BX is a 16 bit register mainly used as base register for memory address calculation, BL indicates the lower 8-bit and BH indicates the higher 8-bit of BX.

- Register CX is used as default counter (looping) and DX is used to hold I/O address during certain I/O instructions. Ex: If the result of multiplication is more than 16 bits the low order bits are stored in AX, the high-order 16 bits are stored in DX register

#### **Segment Registers**

- Intel 8086 is byte organized. Here 1 MB of memory is divided into 16 logical segments. Each segment contains 64 kilobytes of memory. There are four segment register in 8086; Code segment register (CS), Data segment register (DS), Extra segment register (ES) and Stack segment register (SS). Code segment register (CS) points out the starting address of the code segment memory, where the executable program is stored.

- Data segment register (DS): points the starting address of the data segment of the memory where the data is stored. Extra Segment Register (ES) also points the starting address of the extra segment memory locations. These registers act as base registers.

#### **Stack Segment Register (SS)**

By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment. SS register can be changed directly using POP instruction. It is used for addressing stack segment of memory and is used to store stack data. The starting address of the each segment can be obtained from CS, DS, SS and ES registers.

#### **Pointers and Index Registers**

The pointers IP, BP, SP usually contain offsets within the code, data and stack segments respectively.

- Stack Pointer (SP) is a 16-bit register pointing to program stack in stack segment.

- •Base Pointer (BP) is a 16-bit register pointing to data in stack segment. BP register is usually used for based indexed or register indirect addressing. The index registers are particularly useful for string manipulation. SI is used to store the offset of source data in data segment. DI is used to store the offset of destination in data or extra segment.

#### **Status Register**

It determines the current state of the processor. They are modified automatically by CPU after mathematical operations. This allows to determine the type of the result and to determine the conditions to transfer the flow of execution to other parts of the program.

#### Carry flag (CY)

It is set whenever there is a carry or borrow out of the MSB of a result. CY=1, Carry is generated CY=0, Carry is not generated.

**Parity flag (PF)**:It is set if the result has even parity of 1s. If parity is odd, PF is reset.

**Auxiliary carry flag (AC):** Holds a carry after addition or a borrow after subtraction between bit 3 and 4 of the result.

8086 Architecture

NOTES

**Zero flag** (ZF): Indicates the result of an arithmetic or logic operation. It is set if the result is zero

**Sign flag (SF):** Indicates the arithmetic sign of the result after an addition or subtraction. If S = 1, the result is negative. If S = 0, the result is positive.

**Overflow flag (OF):** An overflow condition indicates that a result has exceeded the capacity of the machine when a condition that can occur when signed numbers are added or subtracted.

#### **ControlFlags**

**Trap flag (TF):** Debugging feature of the microprocessor by setting single step mode of execution in the microprocessor. In single step mode the 8086 executes a software interrupt. The interrupt vector table contains certain locations reserved for single step mode.

**Interrupt flag (IF)**: interrupt controls operation. If I = 1, the INTR pin is enabled. If I = 0, the INTR pin is disabled.

**Direction flag (DF)** Controls the selection of increment and decrement for the DI and SI registers during string instructions. If DF=1, the string bytes are accessed from low memory address to high memory address. The contents of SI and DI are decremented. If DF=0, the string bytes are accessed from high memory address to low memory address. The contents of SI and DI are incremented.

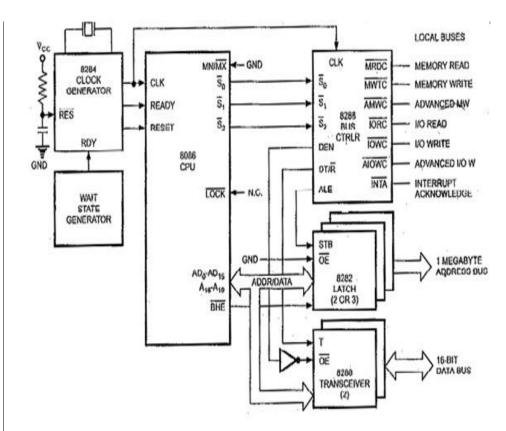

#### 2.5 MAXIMUM MODE FUNCTION OF 8086

In the maximum mode, the 8086 is operated by strapping the  $MN/\overline{MX}$  pin to ground.

- ❖ In this mode, the processor derives the status signal S2, S1, S0. Another chip called bus controller derives the control signal using this status information. In the maximum mode, there may be more than one microprocessor in the system configuration. The components in the system are same as in the minimum mode system.

- ❖ The basic function of the bus controller chip IC8288 is to derive control signals like  $\overline{RD}$  and  $\overline{WR}$  (for memory and I/O devices),  $\overline{DEN}$ ,

$DT/\overline{R}$ , ALE etc. using the information by the processor on the status lines.

❖ The bus controller chip has input lines S2, S1, S0 and CLK. These inputs to 8288 are driven by CPU. It derives the outputs ALE, DEN,

$DT/\overline{R}$ ,  $\overline{MRDC}$ ,  $\overline{MWTC}$ ,  $\overline{AMWC}$ ,  $\overline{IORC}$ ,  $\overline{IOWC}$  and  $\overline{AIOWC}$ .

- ❖ Maximum mode of operation AEN and IOB are generally grounded. DEN pin is usually tied to +5V.

- ❖ INTA pin used to issue two interrupt acknowledge pulses to the interrupt controller or to an interrupting device. <a href="#">IORC</a>, <a href="#">IOWC</a> are I/O</a>

- read command and I/O write command signals respectively.

- ❖ These signals enable an IO interface to read or write the data from or to the address port. The  $\overline{MRDC}$ ,  $\overline{MWTC}$  are memory read command

- and memory write command signals respectively and may be used as memory read or write signals.

- ❖ Here the only difference in timing diagram between minimum mode and maximum mode is the status signals used and the available control and advanced command signals. R0, S1, S2 are set at the beginning of bus cycle.

- ❖ When the 8086 is set for the maximum-mode configuration, it provides signals for implementing a multiprocessor / coprocessor system environment.

- ❖ These are known as local or private resources. Coprocessor also means that there is a second processor in the system. In this, two processors do not access the bus at the same time.

- ❖ One passes the control of the system bus to the other and then may suspend its operation. In the maximum-mode 8086 system, facilities are provided for implementing allocation of global resources and passing bus control to other microprocessor or coprocessor.

Figure 2.4 Maximum mode functions of 8086

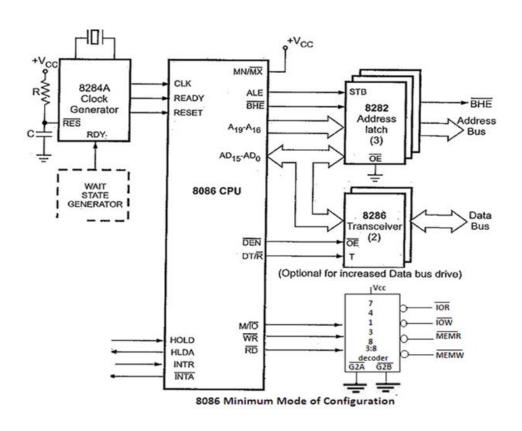

#### 2.6 MINIMUM MODE SYSTEM

- $\triangleright$  Microprocessor 8086 is operated in minimum mode by strapping its MN/ $\overline{MX}$  pin to logic1.

- ➤ In this mode, all the control signals are given out by the microprocessor itself. There is a single microprocessor in the minimum mode system. The remaining components in the system are latches, Transceivers, clock generator, memory and I/O devices.

- Latches are generally buffered output of D-type flip-flops like 74LS373 or 8282. They are used for separating the valid address from the multiplexed address/data signals and are controlled by the ALE signal

- In minimum mode 8086 configuration, transceiver is the bidirectional buffers and they are called as data amplifiers. They are required to separate the valid data from the time multiplexed address/data signals

- They are controlled by two signals namely,  $\overline{DEN}$  and  $\overline{DT/R}$ . The  $\overline{DEN}$  signal indicates the direction of data, i.e. from or to the processor.

- ➤ The opcode fetch and read cycles are similar. Hence the timing diagram can be categorized in two parts, the first is the timing diagram for read cycle and the second is the timing diagram for write cycle.

Figure 2.5Minimum mode functions of 8086

The  $\overline{BHE}$  and AD0 signals are used to select the proper byte or bytes of memory or I/O word to be read or write. The M/ $\overline{IO}$ ,  $\overline{RD}$  and  $\overline{WR}$  signals indicate the type of data transfer.

# **UNIT – III INSTRUCTIONS (8085)**

#### **Structure**

- 3.1 Introduction to instructions for 8085

- 3.2 Instruction set

- 3.3 Software development tools

- 3.4 Sample programs

- 3.4.1 Assembly language program for addition of two 8-bit numbers and store the sum

- 3.4.2 Assembly language program for 8-bit decimal subtraction and store the result

- 3.4.3 Assembly language program to shift an 8-bit number left by one bit

- 3.4.4 Assembly language program to find larger of two numbers

#### 3.1 INTRODUCTION TO INSTRUCTIONS FOR 8085

- An instruction is a binary pattern designed inside a microprocessor to perform a specific function.

- The entire group of instructions that a microprocessor supports is called Instruction Set.8085 has 246 instructions.

- Each instruction is represented by an 8-bit binary value. These 8-bits of binary value is called Op-Code or Instruction Byte.

An instruction determines what specified operation the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

#### 3.2 INSTRUCTION SET

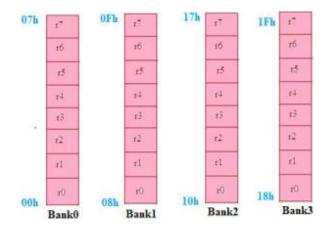

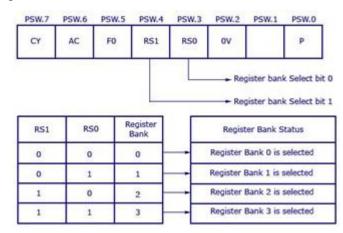

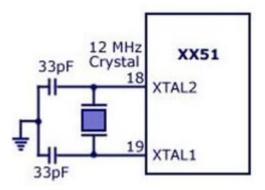

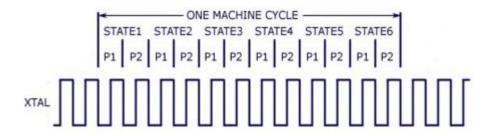

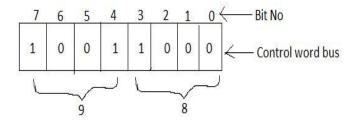

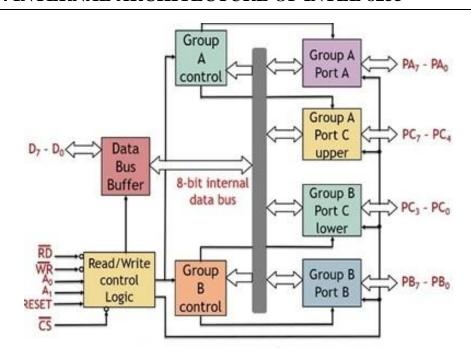

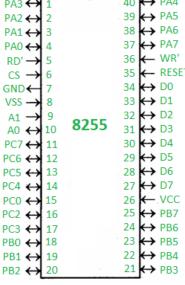

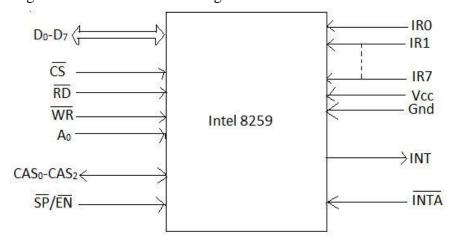

- 8085 instruction set consists of the following instructions: